Nos cuentan que uno de los principales problemas en la escalada hacia potencias de cómputo de exaflops, no es tanto el fin de la vigencia de la ley de Moore como los problemas con la tecnología de fabricación de la RAM que usan los computadores: Concretamente de la DRAM. Y no precisamente la evolución del ancho de banda, sino más bien debido a la latencia. Palabra que repetiré hasta la saciedad en clase.

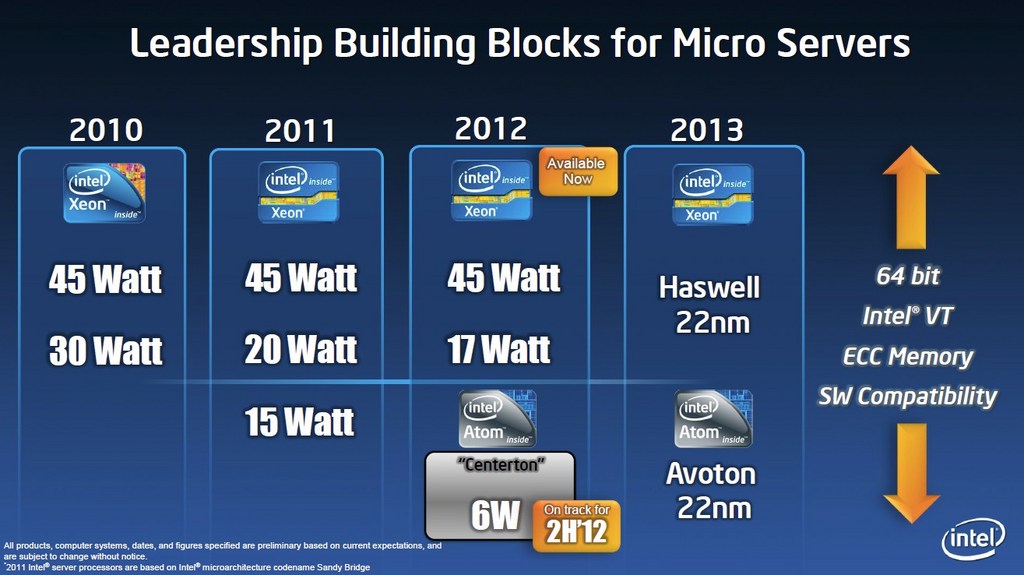

Y no solo la latencia, sino también el consumo:

La meta actual es construir un superordenador con exaflops de potencia de procesamiento, pero con un límite de consumo eléctrico de 20 MW, entre 2018 y 2020. Eso supone, tal vez, cientos de petabytes de RAM. Si usara la mejor DDR3 actual, solo la DRAM consumiría 54 MW. Claramente se necesitan mejoras masivas.

¿Qué hacer entonces?

Toca cambio de tecnología: Últimamente suena mucho la MRAM y los memristores